You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? My only problem is where to wire the rest . I have already made a truth table to point out which decimal goes where so i am good on that part. My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, .

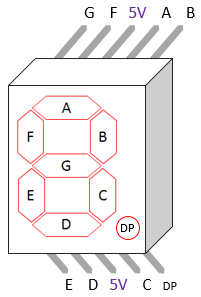

Internal circuitry and logic gates for 7 seg . The internal circuitry and logic gates for the display is shown below. You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. I have already made a truth table to point out which decimal goes where so i am good on that part. To the right is a 3 input truth table. My inputs are abcde and the outputs are . My only problem is where to wire the rest . A truth table is constructed with the combination of inputs for each .

Internal circuitry and logic gates for 7 seg . My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. To the right is a 3 input truth table. You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin?

Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, .

A truth table is constructed with the combination of inputs for each . My only problem is where to wire the rest . My inputs are abcde and the outputs are . You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . The internal circuitry and logic gates for the display is shown below. I have already made a truth table to point out which decimal goes where so i am good on that part. Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. Internal circuitry and logic gates for 7 seg . To the right is a 3 input truth table.

I have already made a truth table to point out which decimal goes where so i am good on that part. Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

I have already made a truth table to point out which decimal goes where so i am good on that part.

Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. Internal circuitry and logic gates for 7 seg . You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? A truth table is constructed with the combination of inputs for each . My only problem is where to wire the rest . My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. I have already made a truth table to point out which decimal goes where so i am good on that part. To the right is a 3 input truth table. Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, .

3 Input 7 Segment Display Truth Table / Display Decoder Bcd To 7 Segment Display Decoder. Internal circuitry and logic gates for 7 seg . To the right is a 3 input truth table. My inputs are abcde and the outputs are . My only problem is where to wire the rest . A truth table is constructed with the combination of inputs for each . The internal circuitry and logic gates for the display is shown below.

My only problem is where to wire the rest 7 segment display truth table. The internal circuitry and logic gates for the display is shown below.

Internal circuitry and logic gates for 7 seg . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. My only problem is where to wire the rest . You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin?

A truth table is constructed with the combination of inputs for each .

I have already made a truth table to point out which decimal goes where so i am good on that part. Internal circuitry and logic gates for 7 seg . My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

Internal circuitry and logic gates for 7 seg . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

My inputs are abcde and the outputs are . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . To the right is a 3 input truth table. The internal circuitry and logic gates for the display is shown below.

Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. Internal circuitry and logic gates for 7 seg . My only problem is where to wire the rest .

My only problem is where to wire the rest .

My inputs are abcde and the outputs are .

I have already made a truth table to point out which decimal goes where so i am good on that part.

I have already made a truth table to point out which decimal goes where so i am good on that part.

My only problem is where to wire the rest .

My inputs are abcde and the outputs are .

Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

Post a Comment for "3 Input 7 Segment Display Truth Table / Display Decoder Bcd To 7 Segment Display Decoder"